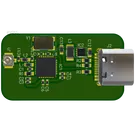

ESP32-C3 Pinout Comparison

5:52

Entendi: você quer a lista completa dos pinos do ESP32‑C3FH4 com os nomes “funcionais” e também como eles aparecem no seu projeto, incluindo sufixos como “__1”. No Flux, quando um mesmo pino lógico tem mais de um “ponto” no símbolo, o editor pode criar “aliases” do mesmo nó elétrico com sufixos como “__1”, “__2” para distinguir gráficos separados, mas todos pertencem ao mesmo pino físico e à mesma rede.

Abaixo segue o mapeamento pino a pino do pacote VFQFN‑32, cruzando:

- Número físico do pino

- Nome funcional comum (datasheet/KiCad-style)

- Nome/uso esperado no projeto atual do Flux (com exemplos de sufixos vistos no seu projeto)

Observações importantes sobre sufixos

- VDD3P3, VDD3P3__1, VDD3P3_CPU, VDD3P3_RTC, VDD_SPI são domínios diferentes ou instâncias repetidas no símbolo. “__1” não muda a função; é o mesmo net/mesmo pino lógico, só uma segunda instância gráfica.

- Para sinais seriais/USB/UART, alguns nós podem aparecer como GPIOxx e/ou nomes alternativos (DN/DP, U0RXD/U0TXD). Conectam ao mesmo pino físico.

Mapa pino a pino (VFQFN‑32)

- Pino 1

- Função: LNA_IN

- No projeto: IC1 LNA_IN

- Pino 2

- Função: VDD3P3 (domínio 3V3 periférico)

- No projeto: VDD3P3 ou VDD3P3__1 sob o net de 3V3

- Pino 3

- Função: VDD3P3 (mesmo domínio 3V3 periférico)

- No projeto: VDD3P3 (pode aparecer com “__1” em outra instância)

- Pino 4

- Função: GPIO0 / XTAL_32K_P

- No projeto: GPIO0/XTAL_32K_P

- Pino 5

- Função: GPIO1 / XTAL_32K_N

- No projeto: GPIO1/XTAL_32K_N

- Pino 6

- Função: GPIO2

- No projeto: GPIO2

- Pino 7

- Função: CHIP_EN

- No projeto: CHIP_EN ligado a R1 via Net 1

- Pino 8

- Função: GPIO3

- No projeto: GPIO3

- Pino 9

- Função: GPIO4 / MTMS

- No projeto: GPIO4/MTMS

- Pino 10

- Função: GPIO5 / MTDI

- No projeto: GPIO5/MTDI

- Pino 11

- Função: VDD3P3_RTC

- No projeto: VDD3P3_RTC

- Pino 12

- Função: GPIO6 / MTCK

- No projeto: GPIO6/MTCK

- Pino 13

- Função: GPIO7 / MTDO

- No projeto: GPIO7/MTDO

- Pino 14

- Função: GPIO8

- No projeto: GPIO8

- Pino 15

- Função: GPIO9

- No projeto: GPIO9

- Pino 16

- Função: GPIO10

- No projeto: GPIO10

- Pino 17

- Função: VDD3P3_CPU

- No projeto: VDD3P3_CPU

- Pino 18

- Função: VDD_SPI

- No projeto: VDD_SPI

- Pino 19

- Função: GPIO12 / SPIHD

- No projeto: GPIO12/SPIHD

- Pino 20

- Função: GPIO13 / SPIWP

- No projeto: GPIO13/SPIWP

- Pino 21

- Função: GPIO14 / SPICS0

- No projeto: GPIO14/SPICS0

- Pino 22

- Função: GPIO15 / SPICLK

- No projeto: GPIO15/SPICLK

- Pino 23

- Função: GPIO16 / SPID

- No projeto: GPIO16/SPID

- Pino 24

- Função: GPIO17 / SPIQ

- No projeto: GPIO17/SPIQ

- Pino 25

- Função: GPIO18 / USB_D−

- No projeto: GPIO18/USB_D−, também pode aparecer como DN; conectado ao USB DN do J2 via Net 17

- Pino 26

- Função: GPIO19 / USB_D+

- No projeto: GPIO19/USB_D+, também pode aparecer como DP; conectado ao USB DP do J2 via Net 16

- Pino 27

- Função: GPIO20 / U0RXD

- No projeto: U0RXD ou GPIO20/U0RXD (Net 9 no seu esquemático mostra U0RXD)

- Pino 28

- Função: GPIO21 / U0TXD

- No projeto: U0TXD ou GPIO21/U0TXD (Net 8 no seu esquemático mostra U0TXD)

- Pino 29

- Pino 30

- Pino 31

- Função: VDDA (analógico)

- No projeto: VDDA (ver com C7)

- Pino 32

- Função: VDD3P3 (periférico)

- No projeto: VDD3P3 (ou VDD3P3__1 dependendo da instância no símbolo)

- Pad exposto (centro)

- Função: GND (PAD térmico)

- No projeto: GND/PAD do IC1, aterrado junto a AGND/PGND no plano

Por que aparecem “VDD3P3__1”, “VDD3P3__2”, etc.?

- São múltiplas instâncias gráficas do mesmo pino/mesmo net no símbolo para facilitar o desenho. Eletricamente é o mesmo nó. O roteamento/PCB considerarão um único pino físico correspondente no encapsulamento.

Quer que eu verifique dentro do seu projeto se todas as redes de alimentação do IC1 (VDD3P3, VDD3P3_RTC, VDD3P3_CPU, VDD_SPI, VDDA) estão realmente ligadas ao mesmo trilho de 3V3 via os indutores/LC previstos e com os capacitores de desacoplamento corretos? Posso revisar e apontar qualquer divergência.

Revisar ligações de power

Verificar filtro LC

Selecionar indutor

Renomear nets

Conferir desacoplamento

163 days

To get started, talk to Flux or create a New Document.

Welcome 👋

Flux helps you build PCBs faster with an AI teammate!

Create your account to collaborate, stay updated, fork your own version, and get instant answers from our AI agent.