Battery Management System Design

1:03

Accessing knowledge base.

To expand from a single-cell to a multi-cell BMS, you’ll need to:

-

Choose a multi-cell charger/BMS IC

- Swap out U1 (RT9525) for a dedicated multi-cell monitor/charger such as TI’s BQ76920 (up to 3 cells) or BQ76930 (up to 10 cells).

- These ICs integrate per-cell voltage sensing, over/under-voltage protection, and passive cell balancing.

-

Add cell-balance circuitry

- Each cell requires a bleed resistor network controlled by the BMS IC to equalize voltages.

- Place balancing MOSFETs or resistors and route individual cell sense lines back to the new BMS IC.

-

Revise voltage dividers and sense nets

- Replace your single VSYS sense resistor divider ([R3]/[R4]) with an array of dividers for each cell.

- Create separate nets (CELL1, CELL2, …) tied to the IC’s CELLx pins.

-

Upgrade connectors and insulation

- Use a higher-voltage pack connector rated for the total stack voltage (e.g., 12.6 V for 3 cells).

- Ensure creepage/clearance distances and high-voltage isolation for ESP32 level shifters or use an isolated ADC interface.

-

Adapt the power-rail architecture

- The TPS62160 input (VSYS) must handle the pack’s full voltage range; check its max VIN (36 V).

- Consider a pre-regulator or a higher-voltage buck if your cell count exceeds its rating.

-

Update firmware and GPIO assignments

- Map the new BMS status flags (OV, UV, CHG, DSG) to ESP32 GPIOs.

- Implement per-cell voltage monitoring and balancing commands in your firmware.

-

Layout and thermal considerations

- Based on Flux KB guidance, “when designing single-cell BMS, compare to 2-cell …” you must now prioritize “component placement to minimize high-voltage loop areas” and ensure copper spacing meets the pack’s max voltage.

- Distribute thermal vias under the BMS IC to dissipate balancing heat.

-

Safety and protection add-ons

- Add input reverse-polarity protection (Schottky or ideal diode) and a TVS array rated to the stack voltage.

- Include an NTC thermistor on each cell group (as supported by many multi-cell BMS ICs).

By following these steps—selecting a multi-cell BMS IC, routing individual cell sense/balance lines, upgrading connectors, and revising power rails—you’ll extend your design to reliably charge, monitor, and balance multiple cells.

222 days

0:59

Considering schematic modifications.

Checking if I can make the changes for you.

Searching for a component.

Searching.

Finished searching for a component.

Planning schematic modification.

Components to Add

| Part Name | Purpose | Manufacturer Part Number | Quantity | Footprint | Datasheet link |

|---|---|---|---|---|---|

| BQ7692000PWR | 3-cell battery monitor & balancer IC to replace the single-cell RT9525 and manage per-cell sensing and balancing | BQ7692000PWR | 1 | TSSOP-20 |

- U1

(RT9525 single-cell charger IC)

222 days

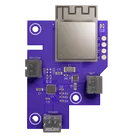

Welcome 👋

Flux helps you build PCBs faster with an AI teammate!

Create your account to collaborate, stay updated, fork your own version, and get instant answers from our AI agent.