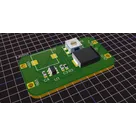

Buffer Summer Splitter Design

0:38

Thinking deeply about your request.

Generating a high-level plan.

You want a Buffer Summer Splitter design.

- I created a plan to define the signal path, capture the electrical requirements, build the schematic, and prepare the PCB layout.

- Since the plan is ready, click Start in the plan bar to begin.

- If you want, I can also update the plan first with details like input/output count, signal type, voltage range, and bandwidth.

Plan

- Develop a circuit design for a 'Buffer Summer Splitter' that can, based upon clarified specifications, provide buffered output, summed inputs, and/or split a single signal to multiple outputs.

#Implementation plan

-

Clarify requirements:

- Request detailed specifications on the intended signal flow to determine if the design should focus on buffering, summing, splitting, or any combination of these functions.

- Capture electrical parameters, including signal type (analog/digital), voltage range, bandwidth, expected impedance levels, and channel counts.

-

Define system architecture:

- Evaluate the need for an analog solution (e.g., op-amp based design) versus a digital approach (e.g., programmable logic) based on the clarified requirements.

- Select and add active components such as low-noise op-amps for buffering and summing functionalities.

-

Schematic design:

- Draft a schematic including distinct sections for buffering, summing, and splitting functions.

- Connect op-amp stages as needed to ensure proper signal conditioning and distribution based on requirements.

-

PCB layout preparation:

- Import and place selected components from the Flux parts library.

- Configure the PCB layout considering power supply routing and component placement to mitigate noise and interference.

#Success criteria

- Obtain complete and unambiguous specifications for buffering, summing, and splitting functionalities.

- A finalized schematic that appropriately partitions the signal conditioning, summing, and splitting functions.

- A PCB layout that is ready for further detailed routing and subsequent manufacturing evaluation.

Set channel count

Add voltage details

Specify op-amp choice

Refine frequency target

35 days

Welcome 👋

Flux accelerates your PCB design with AI.

Create your account to start using this component and bring your ideas to life.

jlamflux

copilot

jlamflux

copilot