Red LED Blink Circuit

1:51

Editing image: "生成一张类似 Cadence Virtuoso 或 GDSII viewer 截图风格的集成电路物理版图概念图。画面要求…"

Looking for "提取与IC物理版图视觉表现相关的信息:模块分区、双向DC-DC管理芯片的主要功能模块、适合在概念版图图中体现的结构要点。" in %E5%82%A8%E8%83%BD%E7%B3%BB%E7%BB%9F%E5%8F%8C%E5%90%91DC-DC%E5%8F%98%E6%8D%A2%E7%AE%A1%E7%90%86%E7%94%B5%E8%B7%AF%E7%AE%80%E8%A6%81%E8%AF%B4%E6%98%8E-74679073-4efc-4f13-abc3-17402bd898ba.docx

Looking for "提取与IC物理版图层次相关的信息:图层名称、分层结构、适合在类似Cadence Virtuoso/GDSII viewer风格图中表现的彩色多层叠加元素。" in %E7%9B%AE%E5%BD%95-de2fccbd-1a04-42ea-b96b-bdcc2b7cb64a.docx

Considering image generation failure.

Generating image: "生成一张类似 Cadence Virtuoso 或 GDSII viewer 截图风格的集成电路物理版图概念图。画面要求…"

Image

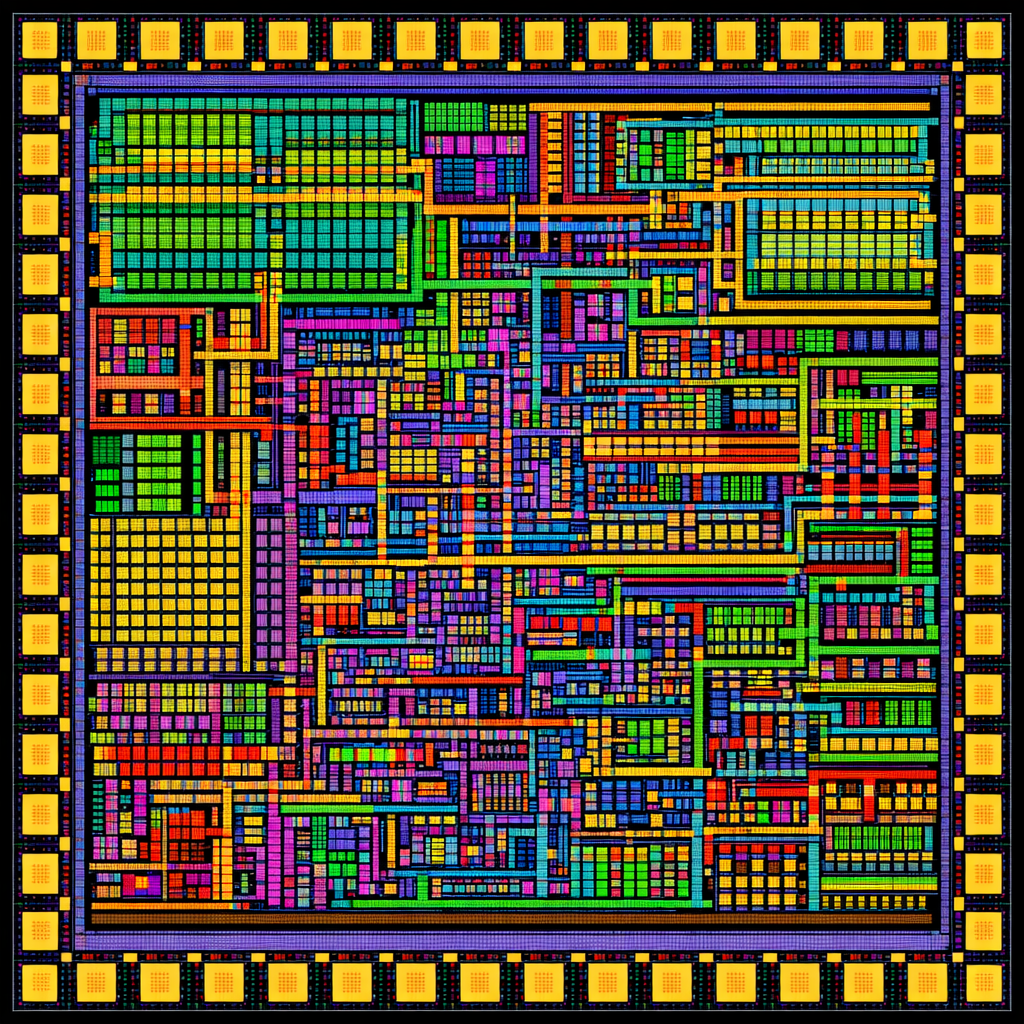

- 双向 DC-DC 管理芯片的功能分区

- 控制核心、ADC、PWM、接口、保护区域

- 多层彩色叠加的版图观感

- 类似目录中提到的层概念:N-well、HV N-well、有源区、Poly、Metal 1、Metal 2、Via、接触孔等

- 这是一张视觉风格概念图

- 不是可制造的真实 GDSII / GDS layout

- 也不是 PCB 图

- 更密、更像真实芯片截图

- 黑底 + 更鲜艳图层色

- 长方形 die 版图

- 带 pad ring / ESD ring / power bus 的版本

- 按你那份双向 DC-DC 芯片功能做 floorplan 风格版本

- Application: bidirectional DC-DC converter management system for energy storage.

- Primary function: manage bidirectional charge and discharge energy flow.

- Control goals: dynamic power regulation, energy optimization, overload protection.

- Performance target: conversion efficiency >= 98%.

- Integrated control intent from source material: MCU-class controller, 16-bit ADC, PWM power control, CAN interface, RS485 interface.

- Environmental intent: industrial operating environment, low static power, good EMI robustness, wide temperature capability.

- Implement the IC-level concept as a PCB-level mixed-signal power management board.

- Partition the design into:

- High-current bidirectional power stage

- Gate-drive / power control stage

- Measurement and ADC front end

- Digital control / supervisory MCU block

- Industrial communications block

- Input/output protection block

- Prefer handoff-ready PCB architecture over transistor-level IC layout.

- Power ingress and protection: fuse, TVS clamp, eFuse / hot-swap protection.

- Bidirectional conversion control: BQ25756 controller with switch-node, feedback, and driver support nets.

- Energy transfer path: inductor and shunt placeholder.

- Supervisory control: C2000 MCU block for telemetry and interface management.

- Communications: CAN transceiver and RS485 transceiver.

- Control support: I2C pull-ups and local decoupling.

- Board outline set to 100 mm x 100 mm rectangle with 3 mm corner radius.

- Stackup set to Standard 4 Layer.

- Board inset margin / universal keepout configured.

- Intended zoning:

- Left / edge ingress: fuse, TVS, eFuse, connector-side protection

- Center power stage: charger/controller, inductor, shunt, bulk capacitors

- Right / lower-noise control area: MCU, CAN, RS485, decoupling

- Interface edge area: CAN / RS485 exits away from switch-node region

- Global baseline trace width: 0.25 mm for control signals.

- Primary power-path target trace width: >= 3.00 mm for protected input and protected bus copper.

- Switch-node target trace width: 2.50 mm with strong spacing from sensitive nets.

- Communications target trace width: 0.25 mm for CAN and RS485 differential lines.

- Keep high-current switching copper compact and isolated from ADC / control traces.

- Keep CAN / RS485 and I2C away from the switching node.

- Use solid internal ground reference under MCU and interface area.

- Reserve copper spreading and thermal relief around fuse, eFuse, controller, shunt, and inductor.

- Missing footprints check passed.

- Airwires remain, which is expected because detailed PCB trace routing has not been completed yet.

Welcome 👋

Flux helps you build PCBs faster with an AI teammate!

Create your account to collaborate, stay updated, fork your own version, and get instant answers from our AI agent.